Description

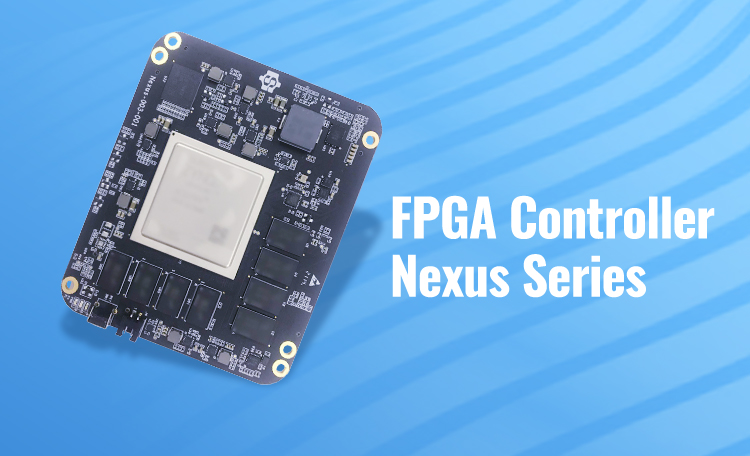

Based on the FPGA technology of Xilinx Zynq UltraScale+ MPSoC, Nexus adopts Xilinx Zynq UltraScale+ and integrates a multi-core ARM Cortex processor, abundant FPGA resources, and high-speed SerDes lanes. Nexus can simultaneously act as a controller, an algorithm accelerator, and a high-speed digital signal processor. SmartGiant also provides customization services to help customers free their hardware, logic, firmware, and software tasks, as well as ODM services from R&D, validation and mass production.

▶ Controllers

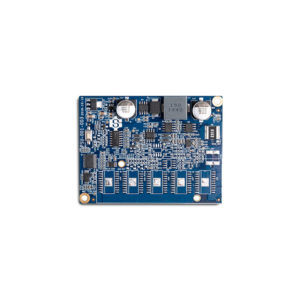

| Controller | FPGA Model & Parameter | Basic Specification |

| SG2625-MU01PC-Zynq 7020 | Xilinx Zynq 7020, Dual-Core ARM Cortex-A9, Atrix-7 85K-Logic Cell: | 1 GB DDR3, 4 GB eMMC, 16 MB Quad SPI Flash, 1 Gb Ethernet, USB 2.0, UART: |

| SG2625-MU02PC-Zynq 7010 | Xilinx Zynq 7010, Dual-Core ARM Cortex-A9, Atrix-7,25K-Logic_Cell; | 1 GB DDR3, 4 GB eMMC, 16 MB Quad SPI Flash, 1 Gb Ethernet, USB 2.0, UART: |

| SG2625-MU03PC-Zynq 7007 | Xilinx Zynq 7007, Single-Core ARM Cortex-A9, Atrix-7,23K-Logic_Cell; | 512 MB DDR3, 4 GB eMMC, 16MB Quad SPI Flash, 1 Gb Ethernet, USB 2.0, UART: |

| Nexus-001 -2EG | Xilinx Zynq UltraScale+ZU2EG, Quad-Core ARM, 103K-Logic_Cell, | 2 GB DDR4, 16 GB eMMC, 1 Gb Ethernet, USB 3.0 Type-C, UART: |

| Nexus-002 -4EG | Xilinx Zynq UltraScale+ZU4EG, Quad-Core ARM, 192K-Logic_Cell, 16 lane Serdes; | 2 GB DDR4, 16 GB eMMC, 1 Gb Ethernet, USB 3.0 Type-C, UART: |

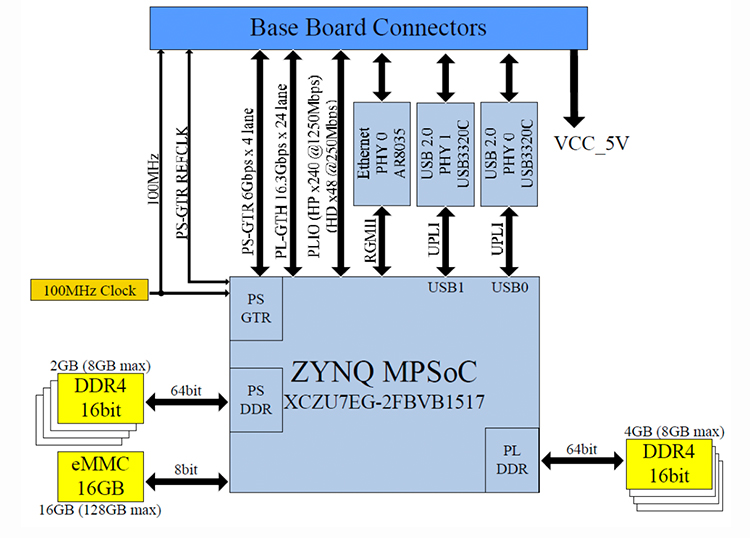

| Nexus-003 -7EG | Xilinx Zynq UltraScale+ZU7EG, Quad-Core ARM, 504K-Logic_Cell; | 2 GB DDR4, 16 GB eMMC, 1 Gb Ethernet, USB 3.0 Type-C, UART; |

▶ Application Scenarios

- FPGA Controller

- Digital Signal Processing

- Algorithm Acceleration

- Emulation & Prototyping

- Data Center

- Industrial & Vision

- Healthcare & Sciences

- Test& Measurement

- Wired & Wireless Communications

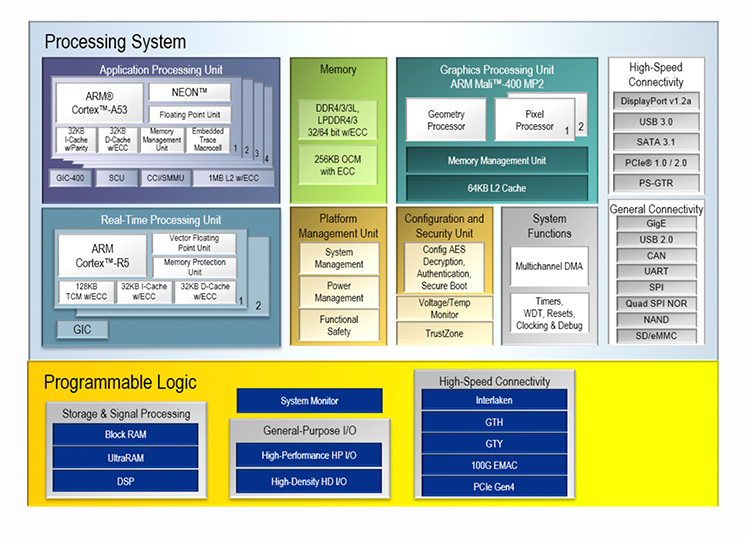

▶ Processing System (PS)

| APU (Application Processing Unit) | Quad ARM®Cortex™-A53

Frequency: 1.5 GHz |

| RPU (Real-Time Processing Unit) | Dual ARM® Cortex™-R5

Frequency: 600 MHz |

| L1 Cache | 32 KB Level 1, 2-way set-associative instruction cache with parity (independent for each CPU) |

| L2 Cache | 1 MB Level 2, 16-way set-associative data cache with ECC (shared between the CPUs) |

| On-Chip Memory | 256 KB on-chip RAM (OCM) in PS with ECC |

| External Memory Interfaces | DDR4, DDR3, DDR3L, LPDDR3, LPDDR4 |

| 8-Channel DMA Controller | 2 DMA controllers for every 8 channels |

▶ Programmable Logic (PL)

| Nexus-003-001 | Nexus-002-4EG | Nexus-001-2EG | |

| MPSoC | XCZU7EG | XCZU4EG | XCZU2EG |

| Programmable Logic Cells | 504 K | 192 K | 103 K |

| Flip-Flops | 461 K | 176 K | 94 K |

| Look-Up Tables (LUTs) | 230K | 88 K | 47 K |

| Total Block RAM | 38 MB | 18 MB | 5.3 MB |

| Programmable DSP Slices | 1728 | 728 | 240 |

| PL SerDes | 24-lane TX/RX, 16.3 Gbps | 16-lane TX/RX, 16.3Gbps | None |

▶ Module Appearance

▶ Nexus-003-001 Hardware Block Diagram

▶ XCZU7EG FPGA SOC (ARM+FPGA) Architecture

The Zynq®UltraScale+™ MPSoC family is based on the architecture of Xilinx UltraScale™ MPSoC. This family of products integrates a feature-rich 64-bit quadcore/dual-core Arm®Cortex™-A53 and dual-core Arm®Cortex™-R5 based processing system (PS) and Zynq®UltraScale™ programmable logic (PL) in a single device. Also included are on-chip memory, multiport external memory interfaces, and a rich set of peripheral connectivity interfaces.